# 전계효과 트랜지스터

FET: Field Effect Transistor

#### FET 종류

- □ 제조방법에 의한 분류

- 접합형 전계효과 트랜지스터 (JFET: Junction Field Effect Transistor)

- MOS FET(Metal Oxide Semiconductor FET): 공핍형, 증가형

- CMOS FET(Complementary MOSFET)

- □ 채널(드레인-소스간의 전류통로)에 의한 분류

- N채널형, P채널형

#### FET와 BJT 비교

#### □ 장점

- ① 동작은 다수 캐리어만의 이동에 의존하므로 단극성소자 (單極性素子, unipolar device)이다.

- ② 접합 트랜지스터에 비해서 큰 입력 임피던스(10<sup>8~</sup> 10<sup>10</sup>[Ω])를 가지고 있으므로 전압증폭소자에 적합하다.

- ③ 잡음특성이 양호하여 소신호를 취급하기 좋다.

- ④ 제조과정이 간단하고 집적회로에서 차지하는 공간이 적어서 집적도 를 아주 높게 할 수 있다.

### □ 단점

- ① 접합 트랜지스터(BJT)에 비해서 동작속도가 느리다

- ② 고주파 특성이 나쁘다

# BJT와 FET 비교

| 항목     | BJT                                              | FET                                                                     |

|--------|--------------------------------------------------|-------------------------------------------------------------------------|

| 기본동작원리 | - 전류로서 전류를 제어.                                   | - 전압(전계)로써 전류를 제어                                                       |

| 반송자 종류 | - Bipolar소자(쌍극성)<br>- 자유전자와 정공이 모두 전도<br>현상에 참여. | - Unipolar 소자(단극성)<br>- 자유전자와 정공 중 하나만이<br>전도 현상에 참여.                   |

| 단자의 명칭 | - Base/Emitter/Collector                         | - Gate/Source/Drain                                                     |

| 장점     | - 스피드가 빠르다.<br>- 전류 용량이 크다.                      | - 입력 임피던스가 크다 온도에 덜 예민하다 제조가 간편하다: IC제조에<br>용이<br>- 동작 해석의 단순(Unipolar) |

| 소자의 구분 | - NPN<br>- PNP                                   | - N 채널<br>- P 채널                                                        |

### FET 용도 및 특징

#### □ 용도

- VHF,UHF 와 같은 고주파 증폭부에서 많이 사용

- MOSFET 는 스위칭 소자(컨버터,인버터)로서 많이 사용

- Maker:삼성, 히다찌, Fairchild, Harris 등

### □ 특징

- FET는 게이트의 인가전압에 의해 채널을 흐르는 전류 (드레인-소스)를 제어하고 동작시 두 개의 다른 형태의 전하(게이트-소스, 드레인-소스)중 둘 중 하나만 이용하는 전압제어소자이지 만 BJT와 같은 전압이득을 제공하지 않음.

- ON일 때 낮은 저항과 OFF일때 높은 저항, 적은 누설전류, 작은 캐패시턴스

- 좋은 주파수 응답 등과 같은 특성들로 인해 MOSFET는 증폭기 , 스위치, 전류원으로 사용.

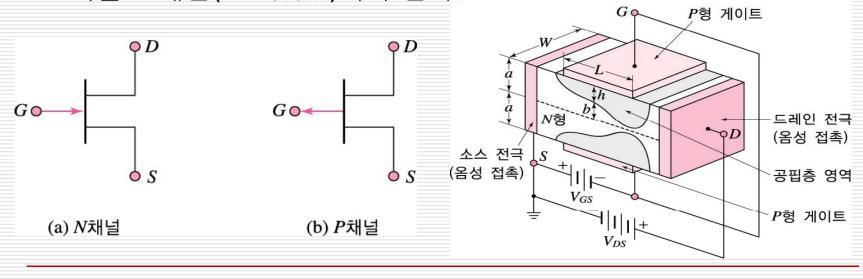

#### JFET 구조

- □ 약하게 도핑된 n형 반도체 막대의 양 옆에 p형 불순물을 강하게 도 핑하여 p+ n접합을 형성

- □ n형 반도체 막대의 양 끝면은 전극이 저항성 접촉으로 만들어져 있고, 이들 사이에 전압을 인가하면 채널 사이에 전류가 흐르게 된다.

- □ 다수 캐리어가 반도체 막대로 흘러 들어가는 쪽의 전극을 소오스(S : source), 다수 캐리어가 반도체 막대로부터 흘러나오는 쪽의 전 극을 드레인(D: drain)이라 한다.

#### JFET 동작특성

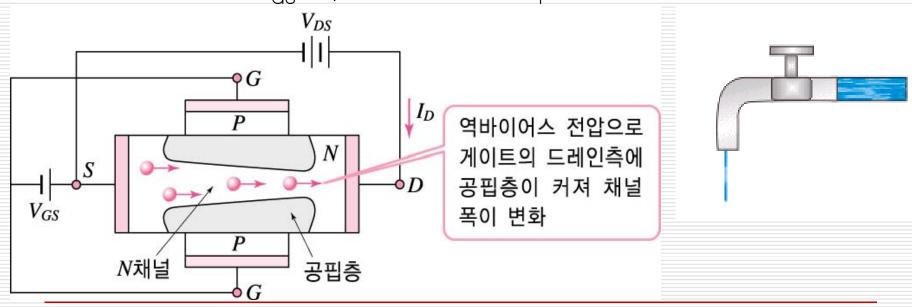

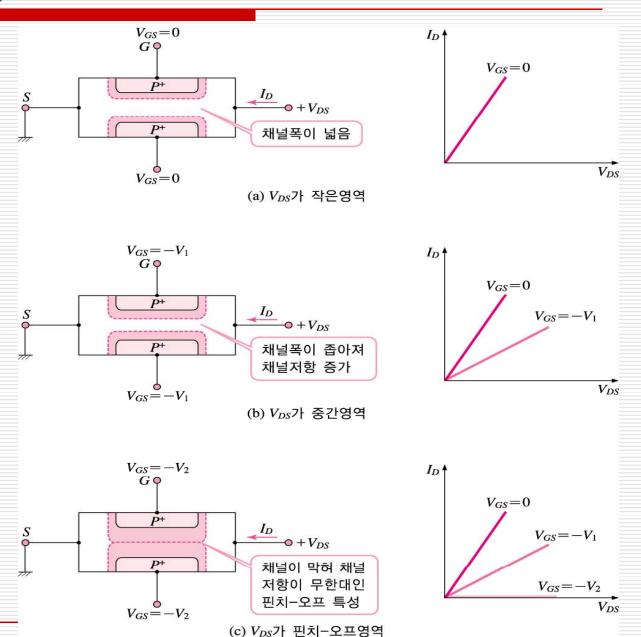

- □ JFET의 실제적인 동작은 D~S 사이를 흐르는 드레인 전류  $I_D$ 가 게이트 전압  $V_{GS}$ 에 의해서 제어

- □ 게이트 접합이 역바이어스가 되도록 게이트 전압(V<sub>GS</sub> < 0)을 인가

- □ 역바이어스된 VGS가 증가하면 공간 전하층은 더욱 넓어져서, 도전 통로인 채널폭은 더욱 좁아진다.

- □ V<sub>GS</sub>를 증대시키면 공간전하층의 폭이 넓어져서 결국은 채널이 완전히 막히게 된다. 이러한 현상을 pinch-off라 한다. 이때의 게이트 -소오스 전압 V<sub>GS</sub>를 pinch-off 전압 V<sub>P</sub>라고 한다.

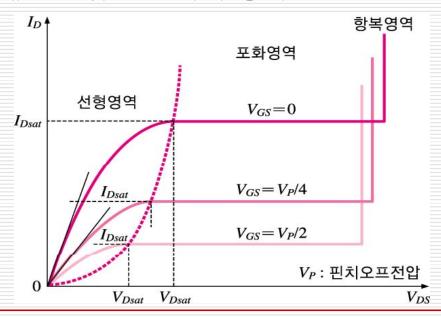

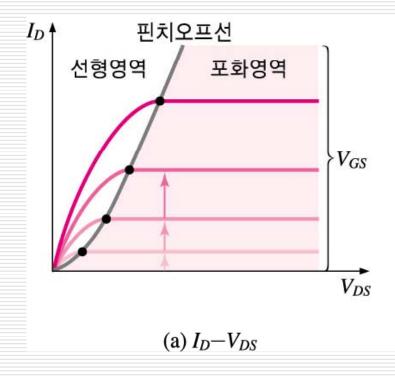

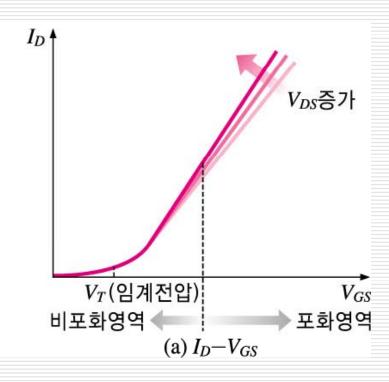

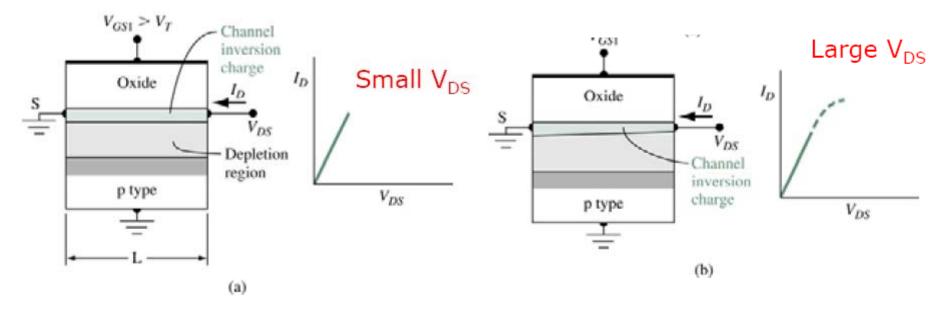

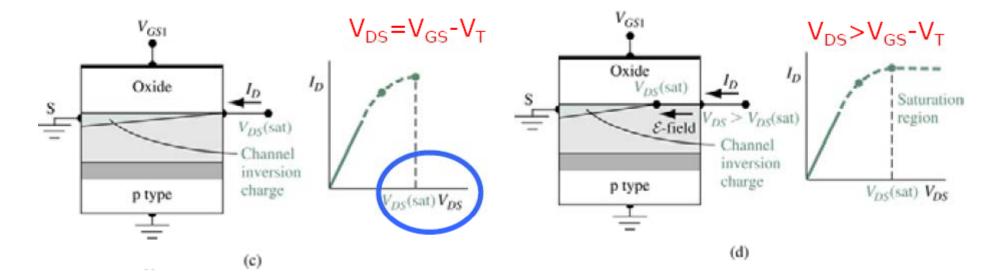

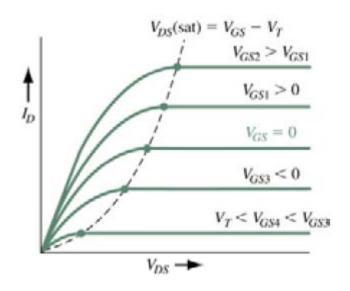

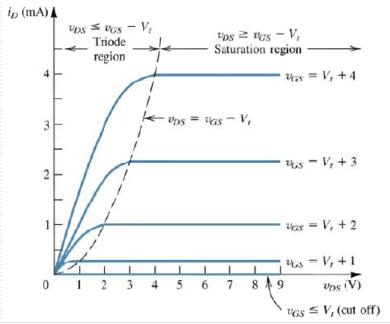

#### I-V 특성

- □ 게이트 전압에 따른 드레인 전류와 드레인 전압과의 관계

- 선형영역(linear region) 드레인 전압은 작으며 I<sub>D</sub>는 V<sub>DS</sub>에 비례

- 포화영역(saturation region) 전류가 V<sub>DS</sub>에 관계 없이 일정 한 영역

- 항복영역(breakdown region) V<sub>DS</sub>의 근소한 증가에 드레인 전류는 급격히 증가

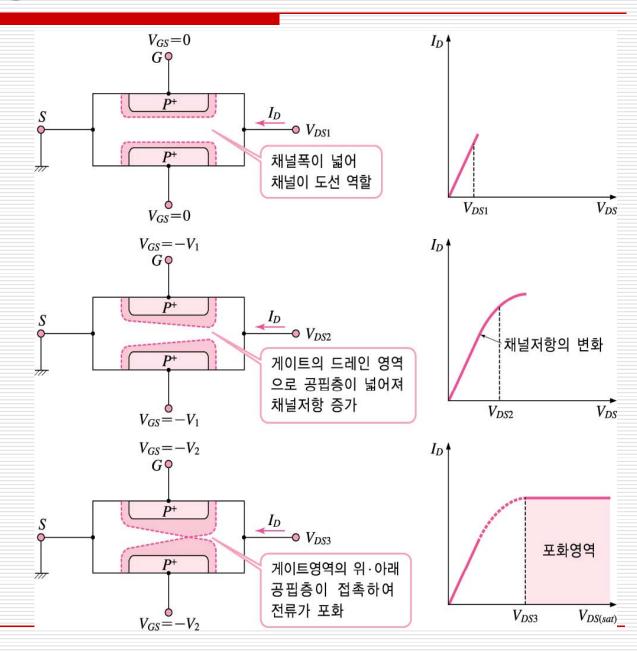

### 동작 - 선형특성

# 동작

전자의 흐름에 관한 특성 (선형특성)

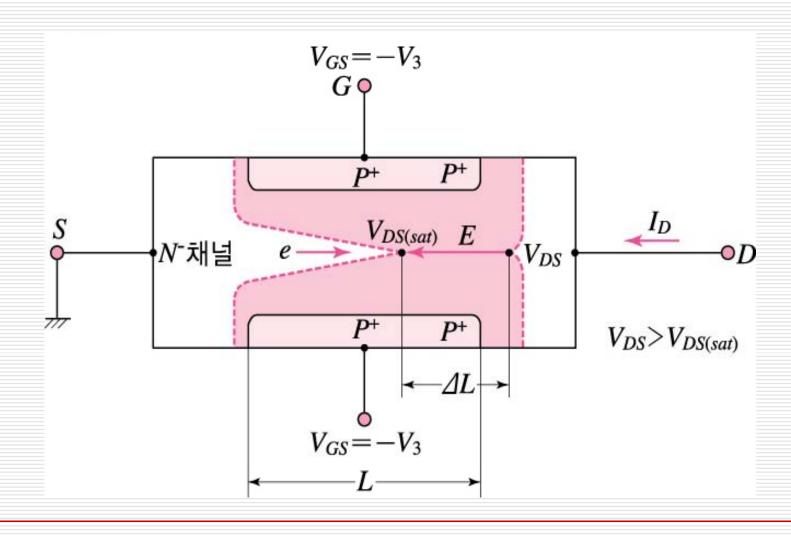

### 동작 - 포화특성

전자의 흐름에

관한 특성

(포화특성)

핀치-오프

(pinch-off)

- 채널의 핀치-오프 (pinch-off) 영역

# I-V (전류 전압) 특성곡선

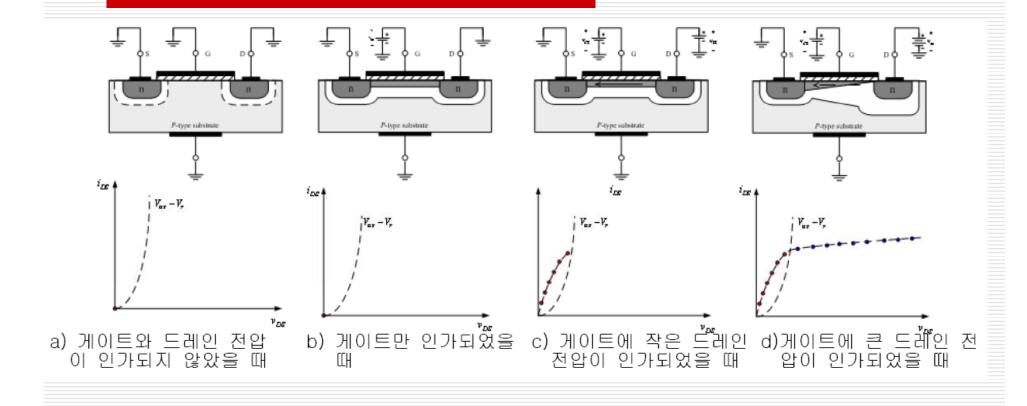

### MOSFET 기본 동작

- □ 기본 트랜지스터 동작

- 게이트 전압에 의해 전자반전층(채널) 형성.

- 소스와 드레인 단자사이에 전류가 발생.

- 소스 단자는 채널에서 흐르는 전하를 공급.

- 드레인 단자는 채널에서 전하를 당기는 역할.

- 전자는 소스에서 드레인으로 이동.

- 전류의 양은 반전층에 있는 전하의 양과 관련.

- 이것은 인가된 전압과 함수 관계를 갖는다.

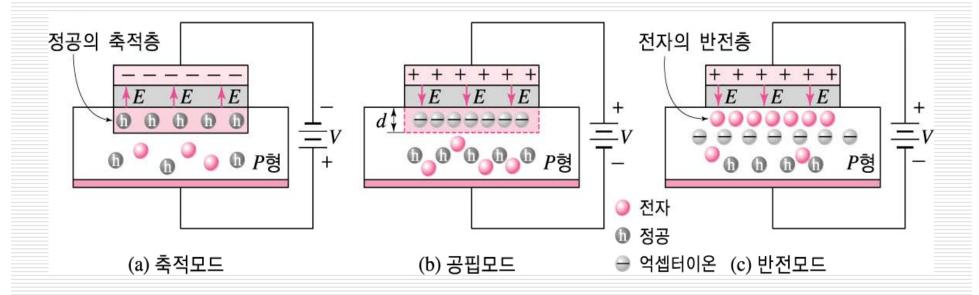

#### ■ MOSFET의 동작

- 축적모드(accumulation mode) 축적층(accumulation layer)

- 공핍모드(depletion mode) 공간전하영역 발생

- 반전모드(inversion mode) 반전층(inversion layer), channel

### 2단자 MOS 커패시터

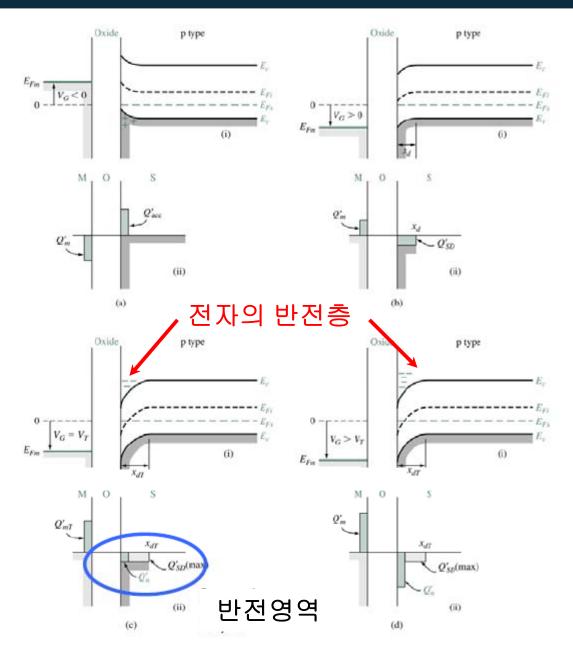

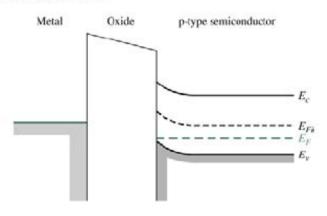

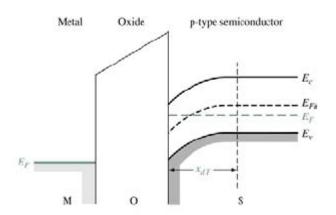

P형 기판을 가진 MOS 커패시터 에너지 밴드 구조

p형 기판을 가진 MOS 커패시터의 게이트(금속)에 충분히 큰 양의 전압을 가하면 반도체 표면은 p형에서 n형으로 반전됨

Fermi 준위는 MOS가 열적 평형상태에 있고 산화막을 통과하는 전류가 없기 때문에 반도체 내에서 일정함

→ Fermi level is constant

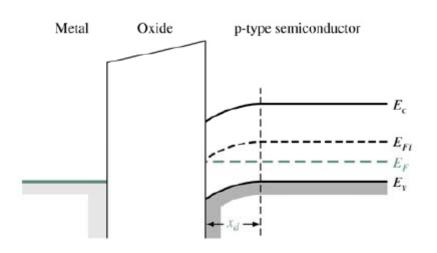

### 2단자 MOS 커패시터

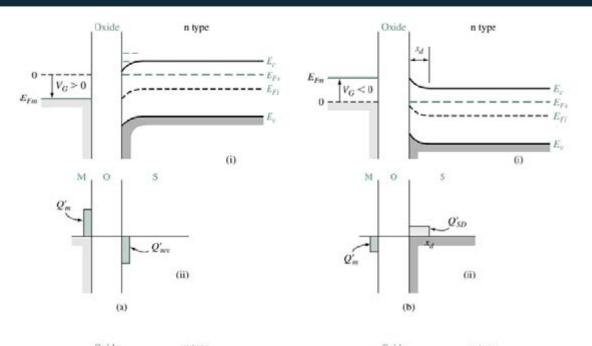

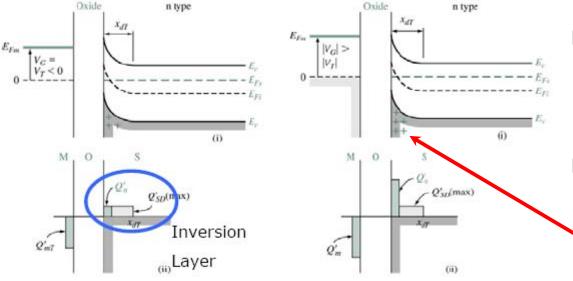

n형 기판을 가진 MOS 커패시터 에너지 밴드 구조

n형 기판을 가진 MOS 커패시터의 게이트(금속)에 충분히 큰 음의 전압을 가하면 반도체 표면은 n형에서 p형으로 반전됨

정공의 반전층

### 2단자 MOS 커패시터

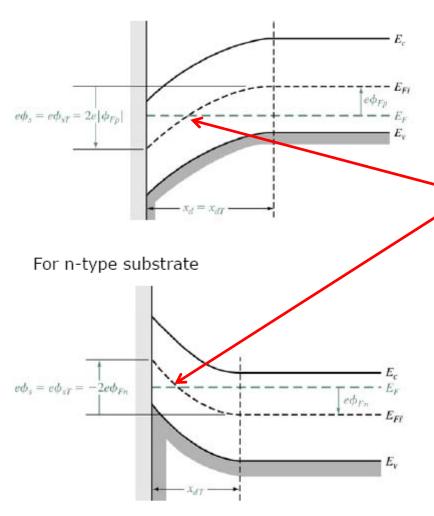

#### For p-type substrate

#### 문턱 반전점

반도체 표면에서의 전자(또는 정공) 농도가 벌크 반도체에서 정공(또는 전자)의 농도와 같을 때 페르미 준위와 진성 페르미 준위의 교차점

### 문턱전압(Threshold Voltage)

문턱 반전점이 생성되기 위해 가해지는 게이트 전압

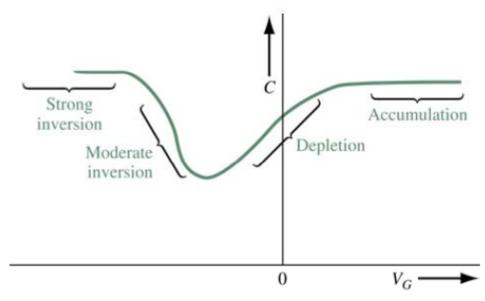

# MOS 커패시터 C-V 특성

#### 1. Accumulation

#### 3. Inversion

#### 2. Depletion

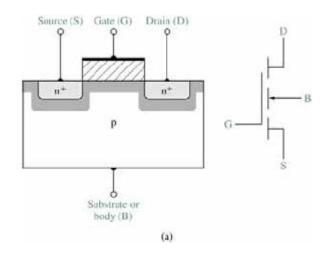

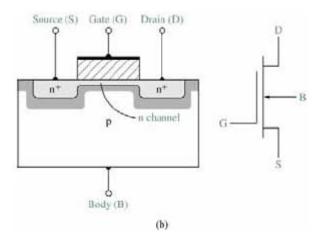

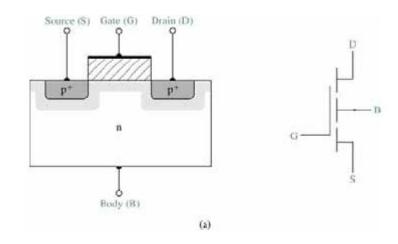

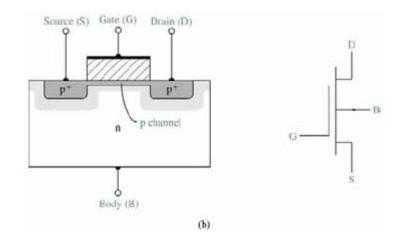

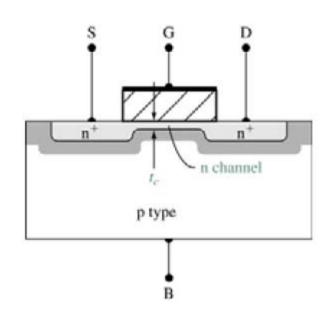

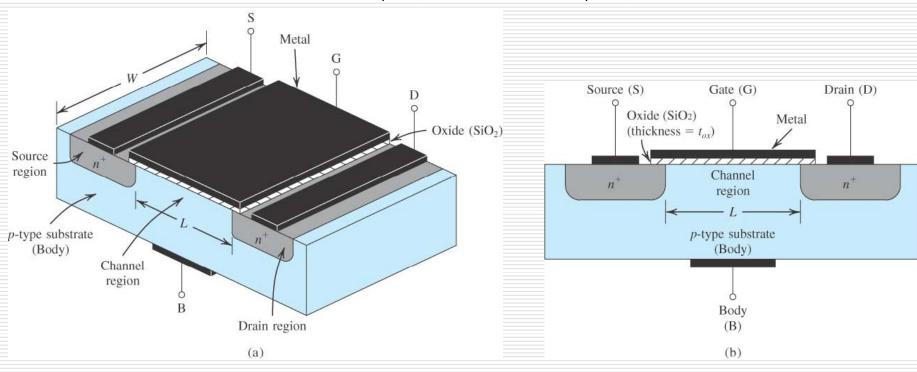

# MOSFET 구조

#### N채널 증가형

N채널 공핍형

#### P채널 증가형

P채널 공핍형

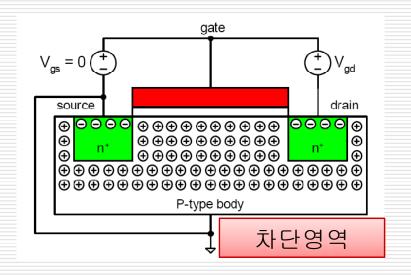

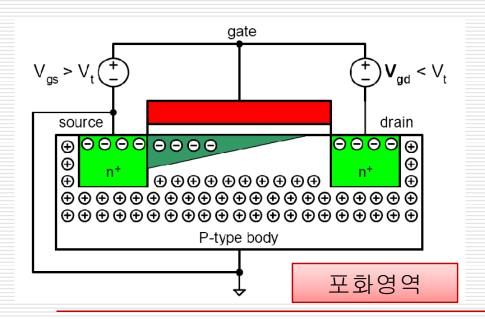

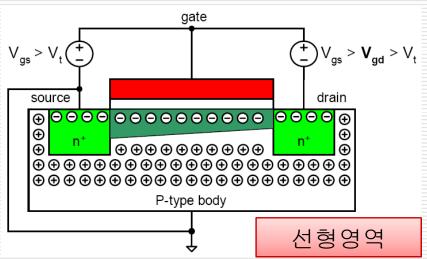

### MOSFET 동작원리

# MOSFET 전류-전압 관계 (I-V curve)

ID vs. VDS curve for an n-channel depletion-mode MOSFET

#### MOSFET

□ 물리적 특성: L=0.1~3µm, W=0.2~100µm, t<sub>ox</sub> = 2~50nm

- □ 3 terminals + Body: Source, Drain, Gate; Symmetric device

- $\square$  NMOS (S&D = n+, G=p) vs. PMOS (S&D=p+, G=n)

#### MOSFET

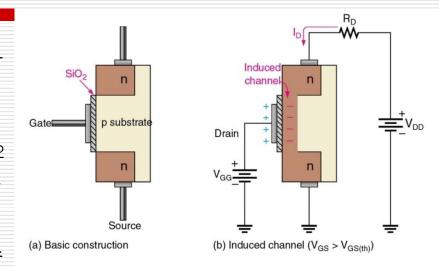

- 금속 산화물 반도체 전계 효과 트랜지스터( Metal Oxide Semiconduct or Field Eeffect Ttransistor; MOSFET)는 FET의 두번째 형태

- pn 접합 구조가 아니라는 면에서 JFET와 상이

- MOSFET의 게이트는 산화실리콘(Sio2) 층에 의해 채널과 격리

- MOSFET는 공핍형(depletion MOSFET; D-MOSFET)과 증가형 (enhancement MOSFET; E-MOSFET)

- E-MOSFET는 채널의 형성되어있지 않음.

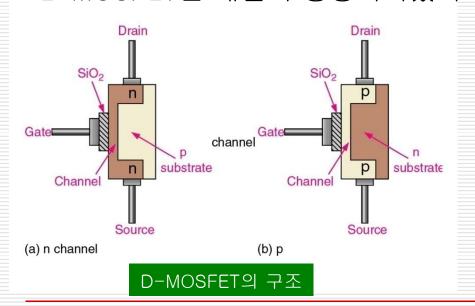

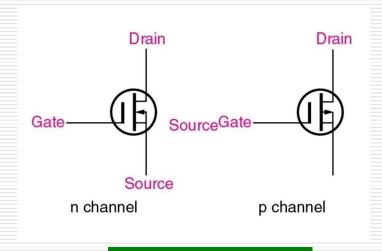

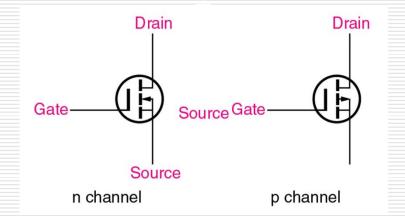

D-MOSFET의 기호

- N채널 증가형(Normally off)

- P채널 증가형(Normally off)

- 게이트 바이어스가 인가되지 않으면 Off상태. 전달특성은 드레인 전류가 N채널의 경우 충분히 큰 양의 게이트 전압에서, P채널의 경우 음의 게이트 전압에서 Tr을 On시킴. 따라서 각각 전자와 홀들의 채널을 만들기 위해서 적당한 크기의 게이트 전압이필요.

- □ N채널 공핍형(Normally on)P채널 공핍형(Normally on)

- Si층의 두께, 도핑농도, 산화막두께,금속 재료등을 조절하여 채널이 게이트에 외부 인가 전압 없이도 채널 형성가능.On으로 동작하기 위해 어떠한 게이트 전압이 필요하지 않음.

- 차단영역에서 동작하기 위해 채널 전자 또는 정공이 제거되야함

. 드레인 전류를 멈추기 위해서 N채널의 경우 음의 전압이 P채널의 경우 양의전압이 필요.

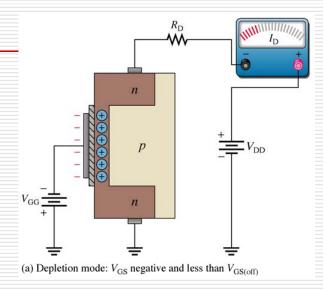

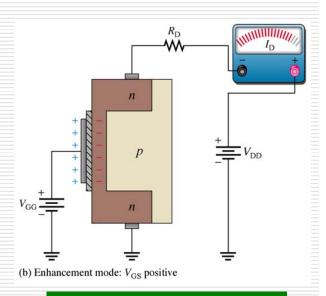

#### 공핍형 MOSFET

- D-MOSFET는 공핍형과 증가형 모드로 분류

- 공핍형 모드는 부(-)의 게이트-소스 전압을 인가하여 동작하고, 정(+)의 전압을 인가하면 증가형 모드로 동작

- 공핍형 모드 게이트에 (-) 전압을 인가하면 채널내의 전도전자를 밀어내고, 그 자리에 양이온이 발생하여 채널내의 전도전자가 부족하게 되고 드레인 전류가 감소하게 되므로 (-) 전압을  $V_{GS(off)}$ 로 하면 채널이 완전 공핍되어드레인 전류가 0

- 증가형 모드 게이트에 (+) 전압을 인가하면 채널내로 전도전자를 끌어 들여 채널내의 전도전자가 증가하게 되어 채널의전도도가 증가함으로써 드레인 전류가 증가

#### D-MOSFET의 동작(공핍

D-MOSFET의 동작(증가

### 증가형 MOSFET

- E-MOSFET는 증가형 모드로만 동작 하고, 구조적 채널 미 존재

- 게이트에 (-) 전압을 인가하면 SiO<sub>2</sub> 층의 접촉면에 얇은 음전하층의 채널 이 형성

- 게이트-소스간의 전압이 증가할 수 록 기판의 전도전자를 더 끌어들여 채 널의 전도도 증가

- 기호에서 점선은 물리적인 채널이 존재하지 않음을 의미

#### E-MOSFET의 구

E-MOSFET의 기호

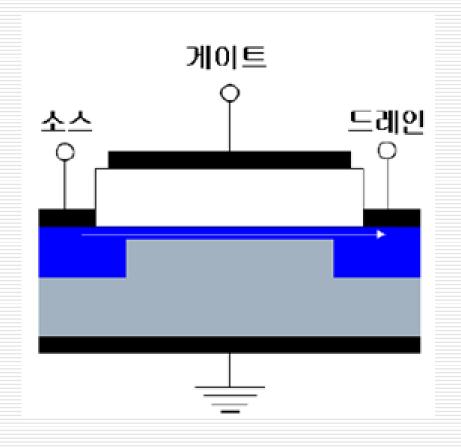

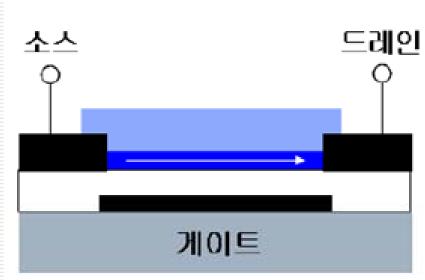

### TFT와 MOSFET의 비교

- □ TFT(Thin Film Transistor)란?

- 박막 트랜지스터는 "절연성 기판 위에 반도체 박막을 입혀 만 든 전계효과 트랜지스터(Field Effect Transistor, FET)"로 정의 할 수 있다.

- TFT는 전계효과 트랜지스터(FET:Field Effect Transistor)인 MOS(Metal Oxide Semiconducter)FET의 일종으로 유리기판위에 비정질 실리콘(amorphous-Silicon) 등의 반도체박막을 형성시켜 여기에 FET구조를 만든 것을 말 한다.

- □ TFT는 FET와 마찬가지로 게이트, 소스, 드레인의 세 단자를 갖는 소자이며 센서, 광소자 등에도 이용되지만 능동 행렬형(active matrix, AM) 액정 디스플레이(Liquid Crystal Display, LCD)의 화소스위치로 주로 사용되고 있다. 최근에 이르러서는 다결정 실리콘 TFT 기술의 개발로 스위치 소자로서 뿐만 아니라 드라이버 회로 (drive IC)를 구성하거나 큰 전류를 다루는 구동 트랜지스터로도 활용되고 있다.

# TFT & MOSFET 구조

MOSFET

**TFT**

- □ TFT 축적모드에서 동작함. 게이트 전압이 인가되면 특정 캐리어의 밀도가 증가. 핵심적으로 전도도의 조절 이 가능한 박막을 사용 해야함.

- □ 절연성이 높은 유리기판위에 Tr이 제조됨. 기존에 다루 던 상부 게이트 구조와 다르게 하부에 게이트를 가지고 저온에서 실리콘 질화 절연 박막을 성장.

- □ 연속적으로 저항성이 높은 진성 실리콘 박막을 성장시 킴.소스와 드레인부에 N+나 P+를 불순물 포함한 실리 콘 박막을 형성.TFT구조를 완성.전류는 소스부터 전자 가 게이트 하부에 생성되는 Si채널층을 거쳐 드레인쪽 으로 흐른다.